Overview

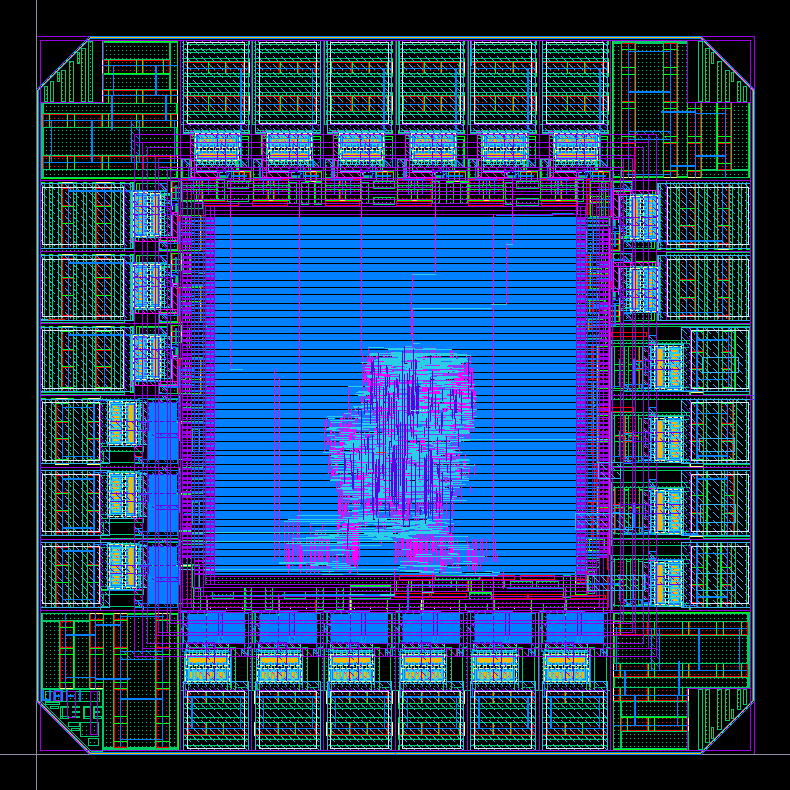

This project built and validated a processor verification toolchain for the open-source MSP430 CPU, targeting a custom low-power cell library. The work encompassed synthesis automation, design-rule verification, scan chain integration for post-silicon testability, and sign-off across two process nodes (65nm and 90nm SOI).

The primary contribution was toolchain development and verification methodology — ensuring the custom cell library was correct, complete, and compatible with standard processor design flows.

Role & Responsibilities

- Lead Physical Design Engineer for the Synchronous openMSP430 implementation

- Synthesized the MSP430 design using Synopsys Design Compiler

- Tested and verified the physical implementation against a custom MTNCL cell library

- Developed the Input/Output logic for both Asynchronous and Synchronous designs, including scan chains for testability

Technology Nodes

The physical design was completed and verified in two process nodes:

- GlobalFoundries 65nm — standard CMOS process

- MITLL 90nm SOI — Silicon-on-Insulator process for extreme environments

Key Outcomes

- Functional verified layout at 65nm and 90nm SOI

- Demonstrated MTNCL library compatibility with standard synchronous processor flows

- Scan chain integration enables post-silicon test coverage